# Amplifying Lower Bounds by Means of Self-Reducibility\*

Eric Allender<sup>†</sup>

Department of Computer Science

Rutgers University

New Brunswick, NJ 08855, USA

allender@cs.rutgers.edu

Michal Koucký<sup>‡</sup>

Institute of Mathematics of the

Academy of Sciences of the Czech Republic

Prague, Czech Republic

koucky@math.cas.cz

October 22, 2009

#### Abstract

We observe that many important computational problems in  $\operatorname{NC}^1$  share a simple self-reducibility property. We then show that, for any problem A having this self-reducibility property, A has polynomial-size  $\operatorname{TC}^0$  circuits if and only if it has  $\operatorname{TC}^0$  circuits of size  $n^{1+\epsilon}$  for every  $\epsilon>0$  (counting the number of wires in a circuit as the size of the circuit). As an example of what this observation yields, consider the Boolean Formula Evaluation problem (BFE), which is complete for  $\operatorname{NC}^1$  and has the self-reducibility property. It follows from a lower bound of Impagliazzo, Paturi, and Saks, that BFE requires depth d  $\operatorname{TC}^0$  circuits of size  $n^{1+\epsilon_d}$ . If one were able to improve this lower bound to show that there is some constant  $\epsilon>0$  (independent of the depth d) such that every  $\operatorname{TC}^0$  circuit family recognizing BFE has size at least  $n^{1+\epsilon}$ , then it would follow that  $\operatorname{TC}^0\neq\operatorname{NC}^1$ . We show that proving lower bounds of the form  $n^{1+\epsilon}$  is not ruled out by the Natural Proof framework of Razborov and Rudich and hence there is currently no known barrier for separating classes such as  $\operatorname{ACC}^0$ ,  $\operatorname{TC}^0$  and  $\operatorname{NC}^1$  via existing "natural" approaches to proving circuit lower bounds.

We also show that problems with small uniform constant-depth circuits have algorithms that simultaneously have small space and time bounds. We then make use of known time-space tradeoff lower bounds to show that SAT requires uniform depth  $d \, {\rm TC}^0$  and  ${\rm AC}^0[6]$  circuits of size  $n^{1+c}$  for some constant c depending on d.

### 1 Introduction

There is consensus in the research community that one of the most challenging and important open problems in computer science is to prove that various computational problems require large circuits in order to be computed. However, there is also a great deal of pessimism in the community, regarding the likelihood of proving such lower bounds on circuit size anytime in the near future. One goal of

<sup>\*</sup>A preliminary version of this paper appeared in the Proceedings of the 23rd IEEE Conference on Computational Complexity, 2008.

<sup>†</sup>Supported in part by NSF Grants CCF-0514155, DMS-0652582, CCF-0830133, and CCF-0832787.

<sup>&</sup>lt;sup>‡</sup>Part of this work was done while visiting DIMACS and Rutgers University partially supported by NSF grant CCF-0514703. Supported in part by grant GA ČR 201/07/P276, project No. 1M0021620808 of MŠMT ČR, Institutional Research Plan No. AV0Z10190503 and grant IAA100190902 of GA AV ČR.

this paper is to suggest that there might be some reason to be more optimistic about prospects for circuit size lower bounds; we show that in certain settings, superpolynomial bounds would follow as a consequence of some very modest-sounding lower bound results (such as a lower bound of size  $n^{1.0001}$ ). Of course, a confirmed pessimist would say that this is merely evidence that even these modest-sounding lower bounds are likely to remain beyond our reach.

### 1.1 The Quest for Circuit Lower Bounds

This paper focuses primarily on the task of proving superpolynomial lower bounds for various well-studied *restricted classes* of circuits, such as NC<sup>1</sup>, TC<sup>0</sup>, and CC<sup>0</sup>[6]. The reader can find definitions of these classes in Section 2, along with a brief discussion of their importance and significance. Here, we recall just a few salient facts:

- Although it seems at first to be an absurdly weak class, CC<sup>0</sup>[6] (the class of problems that can be solved by constant-depth polynomial-size circuit families of MOD-6 gates) has not yet been shown to have less computational power than NP. Some theoreticians suspect that CC<sup>0</sup>[6] cannot even compute the AND function [12, 29]. Showing that AND (or any other problem in NP) lies outside of CC<sup>0</sup>[6] would constitute a significant advance in complexity theory.

- The "majority function" MAJ, which determines if more than half of the input bits are 1, is the canonical representative of the complexity class  $TC^0$ , consisting of the problems computed by constant-depth polynomial-size threshold circuits. Separating the complexity classes  $TC^0$  and  $CC^0[6]$  is equivalent to proving a superpolynomial lower bound on the size of  $CC^0[6]$  circuits computing MAJ.

- NC<sup>1</sup> is the class of Boolean functions that can be represented by Boolean formulae of polynomial size. NC<sup>1</sup> has several natural problems that are complete under very restrictive notions of reducibility; we mention in particular the problem of evaluating a Boolean formula, which we denote by BFE. Separating the complexity classes NC<sup>1</sup> and TC<sup>0</sup> is equivalent to proving a superpolynomial lower bound on the size of constant-depth threshold circuits computing BFE.

The problem of separating these and other circuit complexity classes has remained open for more than two decades. This in itself would be cause for some discouragement about the prospects for progress. Additional grounds for despair were provided by Razborov and Rudich [39], who showed that, if a class of circuits  $\mathcal{C}$  is strong enough to compute pseudorandom function generators, then a wide variety of proof techniques are *incapable* of proving a given problem is too difficult to be computed by circuits in  $\mathcal{C}$ . Since there are constructions of pseudorandom function generators computable in  $TC^0$  that are conjectured to be cryptographically secure [37], this has been viewed as constituting a significant barrier to progress on proving circuit lower bounds.

Although superpolynomial circuit size lower bounds have proved elusive, there has been significant work proving more modest lower bounds. For example, Håstad presents a nearly-cubic lower bound on the formula size for a certain function [27]. Nonlinear lower bounds on branching program size have been presented [3, 14]. The time-space tradeoff results that are surveyed by van Melkebeek [49] give run-time lower bounds of the form  $n^c$  for small-space computations.

However, none of these lower bounds has led to superpolynomial lower bounds. More to the point, there was no expectation that a circuit size lower bound of the form  $n^c$  could *possibly* yield superpolynomial circuit bounds. In this paper, we show that there are several settings where precisely this sort of "amplification" *can* occur.

Moreover, in Section 8 we show that the work of Razborov and Rudich on "Natural Proofs" [39] poses no barrier to proving weak lower bounds of the form  $n^c$ . This can be viewed as holding out some hope of separating circuit classes by proving circuit lower bounds using "natural" proof techniques.

#### 1.2 Our Contributions

The main tool allowing us to obtain our results is self-reducibility of problems. We show that many problems in and around  $NC^1$  (such as BFE, MAJ, AND, and many others) are *strongly downward self-reducible*. Then we show that, for any strongly downward self-reducible set, a lower bound of size  $n^c$  implies a superpolynomial size lower bound.<sup>1</sup>

In particular, we obtain the following corollaries:

**Corollary** If there is some  $\epsilon > 0$  such that AND requires  $CC^0[6]$  circuits of size  $n^{1+\epsilon}$ , then AND  $\notin CC^0[6]$ .

**Corollary** If there is some  $\epsilon > 0$  such that MAJ requires  $CC^0[6]$  circuits of size  $n^{1+\epsilon}$ , then  $CC^0[6] \neq TC^0$ .

**Corollary** If there is some  $\epsilon > 0$  such that BFE requires  $TC^0$  circuits of size  $n^{1+\epsilon}$ , then  $TC^0 \neq NC^1$ .

Let us examine this third corollary more closely. It is interesting to recall that some non-linear lower bounds for BFE are known. Impagliazzo, Paturi, and Saks showed that any depth d  $TC^0$  circuit for PARITY must have  $n^{1+\epsilon_d}$  wires [32] (where  $\epsilon_d = \Omega(1/(2.5)^d)$ ). Since there is a trivial reduction from PARITY to BFE (see the detailed definition of BFE in Section 2), the same size lower bound holds for BFE. In order to separate  $TC^0$  from  $NC^1$ , it would suffice to improve this to a lower bound of size  $n^{1+\epsilon}$  where  $\epsilon$  does not depend on d.

One might reasonably wonder whether it is overly optimistic to expect to prove constant-depth circuit size lower bounds that do not depend on the depth d. Most circuit size lower bounds in the literature (such as those of [25, 52, 30, 40, 46]) do degrade with depth. For instance, the parity function requires depth d AC<sup>0</sup> circuits of size  $2^{\omega(n^{1/(d-1)})}$ , and this is nearly optimal [30]. However, it is important to note that there are exceptions to this trend; Rossman recently proved that, for every constant k, the k-clique problem requires AC<sup>0</sup> circuits with  $\omega(n^{k/4})$  gates *independent* of the depth [44].

Clearly, no proof of  $TC^0 \neq NC^1$  can follow from a PARITY lower bound such as the bound of Impagliazzo, Paturi, and Saks [32], and equally clearly, their argument does not yield a lower bound on the size of depth d  $CC^0[6]$  circuits computing BFE (since  $CC^0[6]$  circuits of linear size compute PARITY). In fact, there seem to be no known superlinear lower bounds for BFE on depth d  $CC^0[q]$  circuits for any q with at least two distinct prime factors. We now turn to the question of obtaining lower bounds for  $CC^0[q]$  and the related class  $AC^0[q]$ , in order to discuss some of our other theorems.

Fortnow showed that SAT does not have logspace-uniform NC<sup>1</sup> circuits of size  $n^{1+o(1)}$  [24]. (Several improvements of this result of Fortnow are presented in [48, Theorem 1.5].) Since we are able to show that modest lower bounds for BFE would yield superpolynomial lower bounds, it is natural to wonder if the same situation holds for SAT. That is, if one could build on the Fortnow lower bound, and show that SAT requires  $AC^0[6]$  circuits of size  $n^{1.01}$ , would it follow that  $NP \neq AC^0[6]$ ? We know of no such implication — and in Section 5 we show that the approach that works for BFE cannot transfer directly to SAT. More specifically, in Section 5 we show that all strongly downward self-reducible sets lie in (uniform) NC. Thus, in order to demonstrate that SAT has the sort of self-reducibility properties that would enable us to amplify modest lower bounds to superpolynomial lower bounds, one would have to first prove that P=NP. (It is still conceivable that one could proceed by arguing that if  $NP = AC^0[6]$ , then SAT has the desired type of self-reduction, but we have not been able to construct such an argument.)

It is interesting to note that Srinivasan has shown [47] that an  $\Omega(n^{1+\epsilon})$  lower bound on the running time of algorithms that compute weak approximations (of the form  $n^{1-o(1)}$ ) to MAX-CLIQUE would imply  $P \neq NP$ . Using his techniques, we show in Section 6 that if  $NP = AC^0[6]$ , then there are  $AC^0[6]$  circuits of size  $n^{1+o(1)}$  that compute  $n^{1-o(1)}$ -approximations to MAX-CLIQUE. We

<sup>&</sup>lt;sup>1</sup>A special case of this general observation (relating only to regular sets) also appears in a survey article by the second author [35]; the present article expands significantly on the related results of [35].

also use a similar argument to obtain lower bounds on the running time of any algorithm reducing MAX-CLIQUE to the problem of computing approximations of MAX-CLIQUE.

Even though we do not know how to separate NP from  $AC^0[6]$  by presenting a lower bound of the form  $n^c$  for the size of  $AC^0[6]$  circuits for SAT, we would nonetheless like to be able to present such a lower bound (as an illustration that current techniques can provide the sort of modest lower bounds that would separate  $NC^1$  from  $AC^0[6]$  if such bounds could be proved for BFE). Although we can not provide such a lower bound, in Section 7 we do provide a lower bound analogous to the Impagliazzo, Paturi, and Saks bound mentioned above; we show that, for every d, there is a constant  $c_d$  such that depth d  $AC^0[6]$  circuits for SAT require size  $n^{1+c_d}$ .

## 2 Preliminaries

### 2.1 Circuit complexity classes

This paper focuses on Boolean circuits and in particular on the circuit class NC<sup>1</sup> and its subclasses. Let us remind the reader of the main definitions, and present some notation. For more background on circuit complexity, the reader is referred to the text by Vollmer [50].

For a function  $f: \{0,1\}^* \to \{0,1\}$  and an integer  $n \ge 1$ ,  $f_n: \{0,1\}^n \to \{0,1\}$  is the restriction of f to inputs of size n.

We begin our discussion of circuits by considering a special case: formulas. A Boolean formula in n variables  $x_1, x_2, \ldots, x_n$  is a rooted tree where each internal node is labeled by some function such as AND, OR or NOT and each leaf is labeled either by one of the input variables  $x_1, \ldots, x_n$  or by a constant zero or one (false or true). Given an input  $x \in \{0,1\}^n$ , one can inductively assign a value to each node of the formula as follows: each leaf labeled by a variable gets the value of that variable, each leaf labeled by a constant gets the value of that constant, and each internal node gets the value of the function that labels it applied to the values of its children. In case where the function labeling a node is not symmetric the order of the children has to be specified. The value (output) of the formula on input x is the value of the root node. Hence a Boolean formula naturally computes a function  $f:\{0,1\}^n \to \{0,1\}$ . The nodes of the formula are generally referred to as gates. The in-degree of a gate is called its fan-in. In addition to the elementary functions AND, OR, and NOT, we will also consider gates computing the function MAJ (which evaluates to one if and only if the strict majority of its inputs is one) and the MOD-q function for an integer  $q \geq 2$  (which is one if and only if the number of its inputs set to one is not divisible by q). The Mod-2 function will also be referred to as the PARITY function ( $\oplus$  function). Sometimes we allow a more complex function to be computed by a gate; a node of a formula can be designated as an *oracle gate*. Typically all the oracle gates in a given formula will compute the same Boolean function  $g:\{0,1\}^* \to \{0,1\}$ , although we allow a single formula to have oracle gates for  $g_m$  and  $g_{m'}$  for  $m \neq m'$ . The oracle should be viewed as a parameter for the formula; for a function g and formula  $\phi$  with oracle gates, the formula  $\phi$  with oracle for g is the formula  $\phi$  where each oracle gate computes the function g. For a set A, an oracle gate for A is an oracle gate computing the characteristic function of A.

A *Boolean circuit* is a generalization of a formula where instead of a rooted tree we allow an arbitrary directed acyclic multi-graph. (We allow multiple edges (or *wires*) between nodes.) The nodes of out-degree zero are the output nodes. This way a circuit can compute a function  $f: \{0,1\}^n \to \{0,1\}^m$ , for integers  $n,m \ge 1$ . In circuits we also allow oracle gates to have several distinct output bits (wires) thus allowing us to have oracle gates for functions  $g: \{0,1\}^m \to \{0,1\}^{m'}$  for m' > 1. (The tree-like nature of formulas imposes the restriction that m' = 1 in a formula.)

The *depth* of a circuit is the length of the longest path from an input node to an output node. The *size* of a circuit is the number of its wires, which is the number of edges in it. We will frequently refer also to the *number of gates* in a circuit,

A circuit computes a function on a fixed number of variables. To compute a function  $f:\{0,1\}^* \to \{0,1\}$  by circuits we need an infinite family of circuits  $\{C_n\}_{n\geq 1}$ , where for each  $n\geq 1$ ,

circuit  $C_n$  computes  $f_n$ . One may abuse notation and say that f is computable by circuits with property  $\gamma(n)$ . Such an expression means that there is a family of circuits  $\{C_n\}_{n\geq 1}$  where each  $C_n$  has property  $\gamma(n)$  and computes  $f_n$ . Similarly, asymptotic statements should be interpreted with respect to the input size; e.g., f is computable by polynomial-size constant-depth circuits means that there is a circuit family  $\{C_n\}_{n\geq 1}$ , polynomial p(n) and constant d, such that each  $C_n$  computes  $f_n$  and has size at most p(n) and depth at most d. Similarly for formulas.

In addition to functions over the binary alphabet  $\{0,1\}$ , we also consider functions over an arbitrary alphabet  $\Sigma$ . In such cases we assume that there is some fixed encoding Bin :  $\Sigma \to \{0,1\}^*$  of symbols from  $\Sigma$  into fixed-length binary strings; circuits for a function over the alphabet  $\Sigma$  operate on inputs encoded symbol-by-symbol by Bin. Furthermore, a circuit for a function with non-Boolean output produces a binary encoding of the output symbol. The definitions of computability by circuits and of all the other terms extend naturally also to this case, however we only require that a circuit computing function f defined on  $\Sigma^*$  operate correctly on binary strings corresponding to binary encodings of strings from  $\Sigma^*$ . Thus, on inputs that do not correspond to binary encoded strings from  $\Sigma^*$ , the circuit may give an arbitrary output. For example a function  $f: \Sigma^* \to \{0,1\}$  is computed by a circuit family  $\{C_n\}_{n\geq 1}$  if for some  $k\geq 1$  there is a binary encoding Bin :  $\Sigma \to \{0,1\}^k$  such that for each  $n\geq 1$ , and each input  $x\in \Sigma^n$ ,  $C_n(\operatorname{Bin}(x))$  outputs  $f_n(x)$ . In this case the size of the input is considered to be n although its binary encoding has length kn. Oracle gates for a function over an arbitrary alphabet  $\Sigma$  also operate on binary encoded strings from  $\Sigma$ , and on invalid inputs we assume that they output all zeros. (We state this convention only in order to make such oracle gates unambiguous; none of our results depends on it.)

A language A is a subset of  $\Sigma^*$  for some finite alphabet  $\Sigma$ . Every language naturally corresponds to its characteristic function  $\chi_A: \Sigma^* \to \{0,1\}$  defined by  $\chi_A(x)=1$  if and only if  $x\in A$ . Vice versa, every function into  $\{0,1\}$  corresponds to a language. We will identify languages with their characteristic functions. We say that A is recognized by  $\{C_n\}_{n\geq 1}$  if its characteristic function is computable by  $\{C_n\}_{n\geq 1}$ .

This allows us to define the following classes of functions.

- NC<sup>0</sup> is the class of functions computable by polynomial-size constant-depth circuits built using fan-in two AND and OR gates and unary NOT gates.

- AC<sup>0</sup> is the class of functions computable by polynomial-size constant-depth circuits built using unbounded fan-in AND and OR gates and unary NOT gates.

- $CC^0[q]$  is the class of functions computable by polynomial-size constant-depth circuits having only unbounded fan-in MOD-q gates.

- AC<sup>0</sup>[q] is the class of functions computable by polynomial-size constant-depth circuits of unbounded fan-in AND and OR gates and unary NOT gates, along with unbounded fan-in MOD-q gates.

- $CC^0$  is the union of all the classes  $CC^0[q]$  (for q > 2).

- ACC<sup>0</sup> is the union of all the classes AC<sup>0</sup>[q] (for  $q \ge 2$ ).

- TC<sup>0</sup> is the class of functions computable by polynomial-size constant-depth circuits of unbounded fan-in MAJ gates and unary NOT gates.

- NC<sup>1</sup> is the class of functions computable by circuits of fan-in two AND and OR gates, and unary NOT gates, having depth  $O(\log n)$ .

- NC is the class of functions computable by circuits of fan-in two AND and OR gates, and unary NOT gates, having depth  $O(\log^k n)$  for a constant k.

Some authors define these classes in terms of *languages* instead of *functions*, and use notation such as  $FAC^0$  or  $FNC^1$ , etc., to refer to the associated class of functions. We prefer the simpler notation, and are confident that no confusion will result. We use the names of the function classes to denote also the corresponding circuit families; e.g., we refer to " $AC^0$  circuit families" or more succinctly to " $AC^0$  circuits".

As presented, these classes are nonuniform, i.e., it is not required that there be an easy way to construct the circuits for inputs of length n. We shall also need to consider logspace-uniform and Dlogtime-uniform versions of these classes [13]. A circuit family  $\{C_n\}_{n\geq 1}$  is logspace-uniform if there is a procedure that runs in logarithmic space and on input  $1^n$  it outputs the description of  $C_n$ . A circuit family  $\{C_n\}_{n\geq 1}$  is *Dlogtime-uniform* if there is a procedure that on input (n,i,r,j,s,t), where n, i, j, r, s are integers encoded in binary and t is a gate type (e.g., AND, OR, NOT, oracle, input, 0,1), runs in time linear in its input size and accepts if and only if the gate of  $C_n$  having label i is of type t and its r-th child is the s-th output bit of the gate labeled j. In case of the gate i being an input gate, the procedure accepts if gate i takes the value of the s-th input bit. Furthermore, the procedure accepts (n, i, j, s, output) if and only if the s-th output bit of gate i is the j-th output bit of the circuit  $C_n$ . We also require that the procedure accepts the input (n, i, d) if and only if d is equal to the fan-in of the gate of  $C_n$  having label i; without this condition it is not always clear that Turing reducibilities defined in terms of uniform circuit families are closed under composition.<sup>2</sup> Thus, for example, Dlogtime-uniform AC<sup>0</sup> is the class of functions computable by Dlogtime-uniform families of AC<sup>0</sup> circuits, or more precisely, the class of functions computable by some Dlogtime-uniform family of circuits of polynomial-size and constant-depth that are built using unbounded fan-in AND and OR gates and unary NOT gates.

A string  $w \in \{0,1\}^*$  of length n is the binary representation of an integer  $m = \sum_{i=1}^n 2^{n-i} w_i$ . The logarithm base two is denoted by  $\log$ .

We use the following convention throughout the paper. Whenever we refer to some real value a (such as  $a = \log n$  or  $a = n^{\epsilon}$ ) in a context where there should be an integral quantity (for instance: "a string of length a") the reader should read it as  $\lceil a \rceil$ .

### 2.2 Reductions and complete problems

The reader is probably familiar with the notion of polynomial-time many-one reducibility  $\leq_m^p$ . Polynomial-time reducibility is an extremely useful tool for classifying NP-complete problems and more generally for classifying the complexity of problems that are not believed to lie in P. However, it is of no use at all in identifying important distinctions among different problems in P. For that, it is necessary to use a more refined tool, such as  $AC^0$  reductions.

For languages A and B we write  $A \leq_m^{AC^0} B$  if there is a function  $r \in \text{Dlogtime-uniform } AC^0$  such that, for all  $x, x \in A$  if and only if  $r(x) \in B$ . More generally, for any class of functions  $\mathcal{C}$ , we say that  $A \leq_m^{\mathcal{C}} B$  if there is a function  $r \in \mathcal{C}$  such that for any  $x, \chi_A(x) = \chi_B(r(x))$ . The function r is called the *many-one reduction of* A to B. We say that A is complete for  $\mathcal{D}$  under  $\leq_m^{\mathcal{C}}$  reductions if  $A \in \mathcal{D}$  and for any language  $B \in \mathcal{D}$ ,  $B \leq_m^{\mathcal{C}} A$ . (Note, we require only *languages* to reduce to A; otherwise no language could be complete for a class that contains any non-Boolean function.) Although  $AC^0$  reductions may seem to be quite restrictive, most natural examples of NP-complete problems remain complete under  $\leq_m^{AC^0}$  reductions. For any class  $\mathcal{C}$  that is closed under  $\leq_m^{TC^0}$  reductions, e.g.  $NC^1$ , any language that is complete for  $\mathcal{C}$  under  $\leq_m^{AC^0}$  reductions is also complete under  $\leq_m^{NC^0}$  reductions [2, 1].

Note that we have defined  $\leq_m^{AC^0}$  reducibility for *uniform* reductions. If A is complete for any of the uniform circuit classes C that we consider under uniform  $\leq_m^{AC^0}$  reductions, then it is also complete

<sup>&</sup>lt;sup>2</sup>There are additional conditions that are required, in order to obtain a satisfactory definition of uniform NC<sup>1</sup>; we refer the reader to the work of Ruzzo, who gives a uniformity condition with the desirable property that uniform NC<sup>1</sup> corresponds to logarithmic time on an alternating Turing machine [45].

for the corresponding *nonuniform* class under nonuniform  $\leq_m^{AC^0}$  reductions. (See the discussion before Proposition 3.)

$NC^1$  has several natural and important problems that are complete under  $\leq_m^{AC^0}$  reductions. We give detailed definitions of three such problems: the word problem over the permutation group  $S_5$  on five elements [11], the Boolean Formula Evaluation problem [17], and s-t-connectivity on directed graphs of width 5.

- (1) The word problem over  $S_5$ . The word problem over the permutation group  $S_5$  is the task of evaluating the product of a sequence of permutations. More generally we define the word problem over a finite monoid M first. A monoid M is a finite set with an associative binary operation and identity element  $1_M$ . We denote the operation of M multiplicatively. The word problem over M is the function  $W_M: M^* \to M$  that assigns to each sequence  $m_1, m_2, \ldots, m_n$  of elements from M their product  $m = m_1 m_2 \cdots m_n$  over M. The empty sequence  $\varepsilon$  is assigned the identity element  $1_M$ . The word problem over  $S_5$  is the word problem  $W_{S_5}$  over the permutation group  $S_5 = \{$  permutations on five elements  $\}$ . The binary operation on  $S_5$  is the composition of permutations; the identity element of  $S_5$  is the identity permutation. (The word problem over  $S_5$  can also be presented as a language consisting of those pairs  $(m, (m_1, \ldots, m_n))$  for which  $m = m_1 m_2 \cdots m_n$ , and technically it is this language that is complete for  $NC^1$  under  $\leq_m^{AC^0}$  reductions but this language has the same complexity as the functional version of the problem that we have presented, and that version is more convenient to work with; working with the language would rather obscure things.)

- (2) The s-t-connectivity problem on directed graphs of width 5. This is an NC<sup>1</sup>-complete variant of s-t-connectivity. We say that a directed graph is of width k if its vertices can be partitioned into layers where each layer is of size at most k, the layers are linearly ordered and every edge goes from vertices of one layer to the vertices of the next layer. Every two consecutive layers of a width 5 directed graph form a bipartite graph and this bipartite graph can be represented by a  $5 \times 5$  adjacency matrix. Thus a width 5 directed graph with n+1 layers can be described by a sequence of  $n \times 5$ adjacency matrices. The s-t-connectivity problem on directed graphs of width 5 is the problem of deciding whether a given vertex s in the first layer is connected by a path to a vertex t of the last layer in a width 5 directed graph. It is more convenient for us to work with the following functional version of connectivity (which has the same complexity as the decision problem), where we ask about connectivity between all vertices of the first and last layers. Let  $\Sigma = \{0,1\}^{5\times 5}$  be the set of binary  $5 \times 5$  matrices. We define W5-STCONN:  $\Sigma^* \to \Sigma$  as follows. For  $A_1, A_2, \ldots, A_n \in \Sigma$ , W5-STCONN $(A_1A_2...A_n)=A$ , where  $A\in\Sigma$  represents the connectivity between the first and last layer of a width 5 directed graph with n+1 layers with adjacency matrices  $A_1, A_2, \ldots, A_n$ . It is a standard fact that A is equal to the product  $A_1A_2\cdots A_n$  over the ring  $(\{0,1\}, OR, AND)$  – and this could also be taken as a formal definition of W5-STCONN. Moreover, one can view W5-STCONN as a word problem over the monoid  $\Sigma$ , where the binary operation is matrix multiplication over the ring  $(\{0,1\}, OR, AND)$  and the identity element of  $\Sigma$  is the identity matrix. This view of W5-STCONN will also be useful for us. Clearly, the word problem over  $S_5$  is a special case of W5-STCONN.

- (3) The Boolean Formula Evaluation problem. Roughly speaking, the Boolean Formula Evaluation problem is the set of formulas that evaluate to true. We will make use of its variant where we focus only on balanced formulas (that is, formulas whose graph is a *complete* binary tree of depth d). Input instances thus consist of a string of  $2^d$  zeros and ones representing the values that label the leaves of the formula, along with a sequence of  $2^d-1$  labels for the internal nodes of the tree. Let  $\Sigma=\{0,1,\wedge,\vee,\oplus\}$ . The set BFE consists of all of the "well-formed formulas" over alphabet  $\Sigma$  that evaluate to 1.

In order to simplify the proof that our construction in Proposition 12 is Dlogtime-uniform, we choose a particular encoding that will be convenient. The "well-formed formulas" consist of strings of the form vx such that for some d, x is a string of length  $2^d$  in  $\{0,1\}^*$ , and v is a string of length  $2^d-1$  in  $\{\wedge,\vee,\oplus\}^*$  representing the labels of the internal nodes of the formula, given in the order specified by the following recursive definition.

If d = 1, then there is only one internal node, so there is no need to specify the order.

If d=2, then the label of the root is listed first, followed by the label of the left child, and then by the label of the right child.

If d>2 and d=2c-1, then the  $2^c-1$  labels of the subtree T of depth c closest to the root are given first, in the order specified for trees of depth c. This is followed by  $2^c$  encodings of the subtrees of depth c-1 whose values feed into T (starting from the leftmost subtree), in the order specified for trees of depth c-1.

If d>2 and d=2c, then the  $2^c-1$  labels of the subtree T of depth c closest to the root are given first, in the order specified for trees of depth c. This is followed by  $2^c$  encodings of the subtrees of depth c whose values feed into T (starting from the leftmost subtree), in the order specified for trees of depth c.

The reader may wonder if it is necessary to be so particular about our encoding of the problem BFE. To some extent, the choice of encoding is crucial. For instance, if a formula were not encoded as a formula, but instead were encoded as an unsorted list of gates and edges, then it is an easy exercise to show that evaluating a formula is complete for L, using the fact that determining whether a vertex u occurs before a vertex v in a directed line graph presented as an unsorted list of edges is complete for L [22]. Thus it is at least important that the formulas in BFE be presented as parenthesized expressions or some similar encoding. The general (not-necessarily balanced) Boolean formula evaluation problem is in  $NC^1$  [17], and thus there are "efficient"  $\leq_m^{AC^0}$  reductions from the general formula evaluation problem to the balanced encoding that we have chosen for BFE, but the reductions that one obtains from known  $NC^1$  algorithms (e.g., [17, 16, 15]) do not appear to be computable by linear-size  $AC^0$  circuits. This is one reason why we do not know how to obtain linear-size strong downward self-reductions for the general Boolean formula evaluation problem, such as we present for BFE. The reason why we include  $\oplus$  as an operation in BFE is so there will be a linear-size reduction from PARITY to BFE, so that the non-linear PARITY lower bounds [32] will immediately carry over to BFE.

Even in this restricted form, BFE is complete for NC<sup>1</sup>. (See, for example, the proof of Lemma 7.2 in [13].)

**Proposition 1** [11, 17]  $W_{S_5}$ , BFE, W5-STCONN are problems complete for NC<sup>1</sup> under  $\leq_m^{\text{NC}^0}$  reductions.

The problem W5-STCONN remains complete for NC<sup>1</sup> if directed edges are permitted *in both directions* between adjacent layers, as well as in the undirected case. The arguments that we present for W5-STCONN also carry over to these variants, with minor technical modifications.

Although  $NC^1$  has several natural complete problems under  $\leq_m^{AC^0}$  reductions, many of the other complexity classes we consider (such as  $TC^0$ ,  $AC^0[q]$ , and  $ACC^0$ ) are not believed to have *any* complete problems under  $\leq_m^{AC^0}$  reducibility. Some of them do, however, have complete problems under  $AC^0$ -Turing reducibility. Our main theorems rely on different variants of Turing reducibility, and thus we need the following general definition.

For any circuit complexity class  $\mathcal{C}$ , we define  $\mathcal{C}$ -Turing reducibility. Let f and g be two functions. We say that  $f \leq_T^{\mathcal{C}} g$  if there is a family of circuits of polynomial size computing f, where the circuits have *oracle gates* for the function g in addition to the collection of gates that is provided in the definition of the circuit class  $\mathcal{C}$ . The family of circuits is called the *reduction of f to g*. We say that f is complete for  $\mathcal{D}$  under  $\leq_T^{\mathcal{C}} f$  reductions if  $f \in \mathcal{D}$  and for any function  $g \in \mathcal{D}$ ,  $g \leq_T^{\mathcal{C}} f$ . It is an

$<sup>^3</sup>$ In this paper, we do not make use of  $NC^1$ -Turing reducibility, and indeed this definition would need to be modified in order to coincide with the definition of  $NC^1$ -Turing reducibility as studied by Cook [20] and Wilson [51] and others. In defining  $AC^k$  reducibility, each oracle gate is considered to have depth 1, as in our definition, but in defining  $NC^k$  reducibility, Cook and Wilson felt that it was more in keeping with the flavor of bounded fan-in circuits to define the depth of an oracle gate to be the logarithm of its fan-in. Using their convention, an  $NC^0$ -Turing reduction could have oracle gates of only bounded fan-in, which is not a very useful notion. In contrast, our definition yields exactly the type of " $NC^0$ -Turing reducibility" that we need in our definition of "pure self-reducibility".

easy observation that languages complete for NC<sup>1</sup> under  $\leq_m^{AC^0}$  reductions are also complete for NC<sup>1</sup> under  $\leq_T^{AC^0}$  reductions.

**Proposition 2** • MAJ is complete for  $TC^0$  under  $\leq_T^{NC^0}$  reductions.

- Mod-q is complete for  $AC^0[q]$  under  $\leq_T^{AC^0}$  reductions.

- AND is complete for ACC $^0$  under  $\leq_T^{\text{CC}^0}$  reductions.

Turing reducibility will be used in the next section, in order to define downward self-reducibility. Reductions can be either uniform or nonuniform. The reader can verify that all of the examples of reductions that we present in this paper are Dlogtime-uniform. It is worth observing that if A is complete for any of the *uniform* classes that we consider under uniform  $\leq_m^{AC^0}$  or  $\leq_T^{\mathcal{C}}$  reductions, then it is also complete for the corresponding *nonuniform* class under nonuniform reductions of the same type. For example, if B is in nonuniform  $NC^1$ , then there is a nonuniform family of Boolean formulae  $\{\phi_n\}_{n\geq 1}$  accepting B. The set  $D=\{(\psi,x):$  a boolean formula  $\psi$  given in infix notation evaluates to 1 on x} is in uniform NC<sup>1</sup> [17, 16] and thus there is a uniform reduction from D to A. Composing this uniform reduction with the nonuniform reduction of B to D that maps x to  $(\phi_x, x)$  yields the desired nonuniform reduction of B to A. Note that, for this example, it is important that C be defined in terms of Boolean formulae, instead of, say, logarithmic depth Boolean circuits, since it is not known whether logarithmic depth Boolean circuits can be evaluated in NC1. A similar construction works also for constant-depth circuits. As an example we briefly explain the case of  $CC^0[q]$ . If B is in nonuniform  $CC^0[q]$  then it is accepted by a family of  $CC^0[q]$  circuits of depth d and size at most  $n^k$ for some  $k, d \ge 1$  and any  $n \ge 2$ . Without loss of generality one may also assume that these circuits are layered and between any two gates there is at most one wire. Consider the set  $D = \{(C, x) : C \in A \}$ is a  $CC^0[q]$  circuit of depth d encoded by a sequence of  $|x|^k \times |x|^k$  adjacency matrices, one for each level of the circuit, such that C(x) = 1. Clearly, D has uniform  $CC^0[q]$  circuits of depth O(d) and size  $n^{O(k)}$ . Hence it reduces to A. Since B nonuniformly reduces to D by transitivity it also reduces nonuniformly to A.

Since completeness results carry over from the uniform setting to the nonuniform setting, we will henceforth slightly abuse notation and simply say that a set A is "complete under  $\leq_{\mathrm{T}}^{\mathcal{C}}$  reductions" even when  $\mathcal{C}$  is a nonuniform class, without explicitly mentioning that the reductions must be nonuniform in this case.

The following fact about Dlogtime-uniform Turing reductions is not entirely obvious, and thus for completeness we provide a proof. Let circuit family  $\{C_n\}$  be a Turing reduction of f to g, and let  $\{D_n\}$  be a Turing reduction of g to h. The *composition* of these reductions is the reduction of f to h that results by replacing each oracle gate of  $C_n$  having fan-in f by f.

**Proposition 3** For any of the classes C defined in this section, the composition of two Dlogtime-uniform  $\leq_T^C$  reductions is a Dlogtime-uniform  $\leq_T^C$  reduction.

*Proof.* Let  $\{C_n\}$  and  $\{D_n\}$  be two Dlogtime-uniform families of reductions. Define a new family  $\{E_n\}$  where  $E_n$  has the following gates:

```

\{i: i \text{ is a non-oracle gate of } C_n\} \cup

```

$\{(i, m, j) : i \text{ is an oracle gate of } C_n \text{ that has fan-in } m \text{ and } j \text{ is a gate of } D_m\}.$

Since the definition of Dlogtime-uniformity ensures that it is easy to recognize the fan-in of an oracle gate, it is routine to establish that the family  $H_n$  (with the obvious connections among gates to implement the composed reduction) is Dlogtime-uniform. For all of the polynomial-size circuit classes C defined in this section, it is immediate that the resulting reduction  $\{H_n\}$  is also a  $\leq_{\mathbb{C}}^{\mathbb{C}}$  reduction.  $\square$

# 3 Downward self-reducibility

In this section we define downward self-reducibility and present several examples of downward self-reducible functions. Intuitively, a function is downward self-reducible if it can be efficiently computed from its own values at shorter inputs. We give a formal definition next.

A C self-reduction for f is a family of oracle circuits witnessing that  $f \leq_T^C f$ , where on input x, the oracle circuit does not feed input x into any of its oracle gates.

Self-reducibility sometimes also goes by the name "autoreducibility." The term "self-reducibility" is more common in those settings (as here) where interest centers on routines that enforce the condition that x is not queried, by ensuring that all queries have length *shorter* than the length of x.

**Definition 4** Let  $f: \{0,1\}^* \to \{0,1\}^*$  be a function, and let C be a class of circuits. Let  $s(n), m(n): \mathbb{N} \to \mathbb{N}$  be functions such that for all n, m(n) < n. We say that  $f_n$  is downward self-reducible to  $f_{m(n)}$  by a C reduction of size s(n) if there is a family of C oracle circuits  $\{C_n\}_{n\geq 1}$  computing f such that for each n,  $C_n$  uses its oracle gates to query f on inputs of size at most m(n), and has at most s(n) wires.

Most of the self-reductions that we present consist of almost no hardware other than oracle gates. We call such reductions "pure"; a *pure self-reduction for* f is an NC<sup>0</sup> self-reduction for f, i.e., a self-reduction where the *only* gates are oracle gates, as well as bounded fan-in AND and OR gates and unary NOT gates.

**Definition 5** Let  $f: \{0,1\}^* \to \{0,1\}^*$  be a function. Let  $s(n), m(n): \mathbb{N} \to \mathbb{N}$  be functions such that for all n, m(n) < n and let  $d \ge 1$  be an integer. We say that  $f_n$  is downward self-reducible to  $f_{m(n)}$  by a pure reduction of depth d and size s(n) if there is a circuit family  $\{C_n\}_{n\ge 1}$  such that for each n,  $C_n$  computes  $f_n$ , is of depth at most d, size at most s(n), and consists of fan-in two AND and OR gates, unary NOT gates and oracle gates that compute function f on inputs of size at most m(n).

We use the term "pure" rather than simply calling them  $NC^0$  reductions, since the term " $NC^0$ " usually refers to computation in which the output depends on at most O(1) bits of the input, and pure self-reductions do not share that property.

We will almost exclusively be interested in functions that are downward self-reducible to inputs of size at most  $m(n) = n^{\epsilon}$ , for some  $\epsilon > 0$ . This notion of downward self-reducibility is essentially identical to what Goldwasser *et al.* call "strong downward self-reducibility" [26]. Hence, if f is downward self-reducible to  $f_{n^{\epsilon}}$  by a pure reduction for some  $\epsilon > 0$ , we will also call it *strongly downward self-reducible*. (Similarly, if f is downward self-reducible to  $f_{n^{\epsilon}}$  by a  $\mathcal C$  reduction for some class  $\mathcal C$ , we will say that f is  $\mathcal C$  strongly downward self-reducible.) For our purposes however, it is important to pay close attention to the size and depth of the reduction.

The rest of this section is devoted to showing that the following problems are strongly downward self-reducible: AND,  $W_M$ , MOD-q, W5-STCONN, MAJ and BFE. We also present somewhat weaker downward self-reducibility results for various types of iterated matrix multiplication problems.

We start with an example that may seem trivial, but is nonetheless useful.

**Proposition 6** For any  $0 < \epsilon < 1$ , AND<sub>n</sub> is downward self-reducible to AND<sub>n</sub><sup>\epsilon</sup> by a Dlogtime-uniform pure reduction of depth  $O(1/\epsilon)$  and size O(n). Similarly for OR.

*Proof.* Consider the AND function. The idea of the proof is simple: form a tree of depth  $O(1/\epsilon)$  from  $\mathsf{AND}_{n^\epsilon}$  gates and assign to each leaf one of the variables. However,  $\epsilon$  and n may be arbitrary so this construction may not be uniform. Thus to provide a Dlogtime-uniform construction one has to be careful about the details. We provide a more detailed construction below to demonstrate the necessary techniques. A reader familiar with the issues of uniformity may want to skip the rest of the proof. Let an integer k satisfy  $2^{k-1} < 1/\epsilon \le 2^k$ . If  $n < 4^{2^k}$  then a tree of  $\mathsf{AND}_2$  gates can be used to compute  $\mathsf{AND}_n$ . So assume for the rest of the proof that  $n \ge 4^{2^k}$ . Pick the largest integer  $\ell \ge 1$

such that  $2^\ell \leq n^{1/2^k}$  and the smallest integer m such that  $n < (2^\ell)^m$ . We will use  $\mathrm{AND}_{2^\ell}$  gates to build the circuit. We will label gates of the circuit by labels from  $\{0,1,\ldots,m\} \times (\{0,1\}^\ell)^m$ . Not all labels will be valid; some labels will be unused. We describe the valid labels together with the associated gates next. Let  $n_1, n_2, \ldots, n_m \in \{0,1\}^\ell$  be such that  $n_1 n_2 \cdots n_m$  is the  $\ell m$ -bit binary representation of n-1 padded with leading zeros if necessary. Consider  $w_1, w_2, \ldots, w_m \in \{0,1\}^\ell$ ,  $w=w_1w_2\cdots w_m$  and  $d\in \{0,1,\ldots,m\}$ . (d,w) represents a valid label in any of the following cases:

- 1. If d=0 and  $w_1=w_2=\cdots=w_m=0^\ell$  then (d,w) is the label of the single output  $AND_{2^\ell}$  gate with inputs from gates labeled by  $(1,w_1'w_2\cdots w_m)$  for any  $w_1'\in\{0,1\}^\ell$ .

- 2. If 0 < d < m,  $w_1 w_2 \cdots w_d$  precedes or is equal to  $n_1 n_2 \cdots n_d$  in the lexicographical order and  $w_{d+1} = w_{d+2} = \cdots = w_m = 0^\ell$  then (d, w) labels an  $AND_{2^\ell}$  gate with inputs from gates labeled by  $(d+1, w_1 w_2 \cdots w_d w'_{d+1} w_{d+2} \cdots w_m)$  for any  $w'_{d+1} \in \{0, 1\}^\ell$ .

- 3. If  $0 < d \le m$ ,  $w_1 w_2 \cdots w_{d-1} = n_1 n_2 \cdots n_{d-1}$ ,  $n_d$  precedes  $w_d$  in the lexicographical order and  $w_{d+1} = w_{d+2} = \cdots = w_m = 0^\ell$  then (d, w) labels a gate with constant one.

- 4. If d=m,  $w_1w_2\cdots w_m$  precedes or is equal to  $n_1n_2\cdots n_m$  in the lexicographical order then (d,w) labels an input gate associated with *i*-th input variable, where i-1 is represented by w in binary.

No other label is used. Since  $\epsilon$  is a constant, k is also a constant. One can verify easily from the description of the gate labeling that the connectivity language for the circuit with respect to this labeling is decidable by a Dlogtime procedure. (Given n in binary, one can find  $\ell$  and m in time linear in the binary representation of n. Incrementing and decrementing a number in binary representation can also be done in time linear in the length of the binary representation. All other operations are clearly in linear time assuming our Dlogtime machine has at least two tapes.) One can also easily verify that the described circuit computes exactly  $AND_n$ .

We claim that it contains O(n) wires. Indeed, the number of wires between bottom level of AND gates and inputs is at most  $n+2^\ell$ . The layer one up contains at most  $n/2^\ell+2^\ell$  wires, the next one  $n/(2^\ell)^2+2^\ell$ , and so on. Thus the number of wires in the circuit is at most  $2n+(m+1)2^\ell$ . Since  $\epsilon<1$ , we have that  $k\geq 1$  and hence  $2^\ell\leq \sqrt{n}$ . Furthermore,  $2^{\ell(m-1)}\leq n$  so,  $m\leq 1+\log n$ . Thus the number of wires in the circuit is bounded by  $2n+\sqrt{n}\cdot(2+\log n)$ .

The case of AND and OR can be further generalized to word problems over finite monoids.

**Proposition 7** For any finite monoid M and any  $0 < \epsilon < 1$ ,  $(W_M)_n$  is downward self-reducible to  $(W_M)_{n^{\epsilon}}$  by a Dlogtime-uniform pure reduction of depth  $O(1/\epsilon)$  and size O(n).

The proof is essentially the same as for AND and OR; one uses gates computing  $W_M$  on inputs of size  $\leq n^{\epsilon}$  and constants for the binary encoding of  $1_M$ . If for an integer  $q \geq 2$  we consider the monoid  $Z_q = (\{0,1,\ldots,q-1\},+(\operatorname{mod} q))$  then we obtain the next corollary.

**Corollary 8** For any  $0 < \epsilon < 1$ ,  $(\text{MOD-}q)_n$  is downward self-reducible to  $(\text{MOD-}q)_{n^{\epsilon}}$  by a Dlogtime-uniform pure reduction of depth  $O(1/\epsilon)$  and size O(n).

*Proof.* Clearly, MoD-q can be computed using  $W_{Z_q}$ . The other way around is also true: one can compute  $W_{Z_q}$  using MoD-q. The proof of the corollary consists of showing how  $(W_{Z_q})_\ell$  can be computed using gates for  $(\text{MoD-}q)_\ell$  and then applying the previous proposition on  $W_{Z_q}$ . A reader familiar with the issue of conversion between  $(\text{MoD-}q)_\ell$  and  $W_{Z_q}$  may want to skip the rest of the proof.

Let  $b \geq 1$  be a constant, Bin :  $Z_q \to \{0,1\}^b$  be an arbitrary injective function, and  $\ell > 4q$  be an integer. We show how to use  $(\text{Mod-}q)_\ell$  gates to compute  $(W_{Z_q})_\ell$  encoded by Bin. Let  $x_1, x_2, \ldots, x_\ell \in Z_q$  be an input to  $W_{Z_q}$  and  $y_1, \ldots, y_{\ell b}$  be its encoding by Bin. We will build

a circuit that takes  $y_1, \ldots, y_{\ell b}$  as its input and outputs  $z_1 \cdots z_b$ , where  $z_1 \cdots z_b$  is the encoding of  $\sum_{i=1}^{\ell} x_i \pmod{q}$  by Bin. The circuit will be of constant depth (depending only on Bin and q) and use  $O(\ell)$  bounded fan-in AND, OR and NOT gates and q MOD-q gates of fan-in  $\ell$ . The circuit computes as follows.

Let  $m=\lceil \ell/q \rceil-2$ . Partition arbitrarily  $\{1,\dots,\ell\}$  into non-empty sets  $S_1,S_2,\dots,S_m$  of size at most 2q. Since  $\ell>4q$ , this is possible. For each  $i\in\{1,\dots,m\}$ , let  $w_i=1^{\sum_{j\in S_i}x_j(\operatorname{mod} q)}0^{q-\sum_{j\in S_i}x_j(\operatorname{mod} q)}$ . Clearly,  $\sum_{i=1}^m\sum_{j=1}^q(w_i)_j=\sum_{i=1}^\ell x_i(\operatorname{mod} q)$ . As q and b are constant,  $w_1w_2\cdots w_m$  can be computed from  $y_1,\dots,y_{\ell b}$  by a circuit of constant depth using  $O(\ell)$  fan-in two AND and OR gates and unary NOT gates.

For  $j=0,\ldots,q-1$ , let  $g_j$  be a MOD-q gate of fan-in  $\ell$  that takes as its input  $w_1w_2\cdots w_m0^j1^{q-j}$  padded with zeros to the length of  $\ell$ . Clearly,  $g_j$  evaluates to zero if and only if  $\sum_{i=1}^\ell x_i=j \pmod q$ . Hence, the output of  $g_0,\ldots,g_{q-1}$  uniquely determines  $\sum_{i=1}^\ell x_i \pmod q$ . The output of  $g_0,\ldots,g_{q-1}$  can thus be processed by a constant size circuit consisting of bounded fan-in AND, OR and NOT gates to compute  $\mathrm{Bin}(\sum_{i=1}^\ell x_i \pmod q)$ . This gives the desired circuit for computing  $(W_{Z_q})_\ell$  encoded by Bin. (For  $\ell < 4q$  one can build a constant-depth circuit computing  $(W_{Z_q})_\ell$  using fan-in two AND gates and unary NOT gates.)

By Proposition 7, there are constants b,k and a function  $\mathrm{Bin}:Z_q\to\{0,1\}^b$  such that for all n large enough, there is a circuit  $C_n$  of depth  $\leq k/\epsilon$  with  $\leq kn$  wires that computes  $(W_{Z_q})_n$  encoded by  $\mathrm{Bin}$  using fan-in two AND and OR gates, unary NOT gates and gates for  $(W_{Z_q})_\ell$  encoded by  $\mathrm{Bin}$ , for  $\ell \leq n^\epsilon$ . Take  $C_n$  and replace each gate for  $(W_{Z_q})_\ell$  by the circuit constructed in the preceding paragraph to obtain a circuit  $C'_n$  computing  $(W_{Z_q})_n$ . The circuit  $C'_n$  consists of fan-in two AND and OR gates, unary NOT gates and  $(\mathrm{MOD}\text{-}q)_\ell$  gates, for  $\ell \leq n^\epsilon$ . Since each  $(W_{Z_q})_\ell$  gate of fan-in  $\ell b$  is replaced by a constant-depth circuit that uses  $O(\ell)$  wires, the depth and the number of wires of  $C'_n$  are only a constant factor larger than that of  $C_n$ .

If we encode an input  $v_1, v_2, \ldots, v_n \in \{0, 1\}$  symbol by symbol by Bin and we feed the resulting string into the circuit  $C'_n$  we obtain  $\sum_{i=1}^n v_i = j \pmod{q}$  encoded by Bin. From this encoded value one can decode the output of MoD-q on input  $v_1, \ldots, v_n$ . Hence using O(n) additional fan-in two AND and OR gates and unary NOT gates one can convert the circuit  $C'_n$  into a constant-depth circuit for  $(\text{MoD-}q)_n$ . The overall size of the circuit will be linear in n.

One can verify that the construction can be made Dlogtime-uniform. Indeed, the circuit computing  $W_{Z_q}$  using Mod-q gates can be made Dlogtime-uniform, and its gate labeling can be concatenated with the labeling of gates in  $C_n$  to obtain a gate labeling of  $C'_n$ . Additional labels can be used for gates calculating the Bin encoding and decoding of input and output of  $C'_n$ . The details of these constructions are rather straightforward and we leave them to the interested reader.

Because of the connection between W5-STCONN and word problems over monoids we also obtain:

**Proposition 9** For any  $0 < \epsilon < 1$ , W5-STCONN<sub>n</sub> is downward self-reducible to W5-STCONN<sub>n</sub> by a Dlogtime-uniform pure reduction of depth  $O(1/\epsilon)$  and size O(n).

We can prove a similar self-reducibility claim also for MAJ. This time the proof is a little bit more involved and uses the following lemma.

**Lemma 10** There is a constant d such that for any  $1 \le \ell \le m$  there is a Dlogtime-uniform depth d circuit family with at most  $4\ell m$  gates (consisting of fan-in two AND gates, unary NOT gates and oracle gates for MAJ<sub>2m</sub>), taking as its input  $\ell$ -bit binary representations of integers  $y_1, \ldots, y_m$ , and producing as output a sequence of integers  $z_1, \ldots, z_\ell$  each represented by  $\ell + \log(m+1)$  bits such that  $y_1 + y_2 + \cdots + y_m = z_1 + \cdots + z_\ell$ .

*Proof.* First, observe that we can compute AND<sub>m</sub> and OR<sub>m</sub>, using a gate for MAJ<sub>2m</sub> and constants 0 and 1. For  $j=1,\ldots,\ell$ , let  $z_j=2^{\ell-j}\sum_{i=1}^m(y_i)_j$ . It follows from the definition of binary

representation that  $y_1+y_2+\cdots+y_m=z_1+\cdots+z_\ell$ . Thus we only need to show how to compute the  $(\ell+\log(m+1))$ -bit binary representation of  $z_1,\ldots,z_\ell$  from binary representation of  $y_1,\ldots,y_m$ . (Note each of the representations of  $z_1,\ldots,z_m$  has  $\ell$  of its bits always set to zero.)

Fix  $j \in \{1,\dots,\ell\}$ . Let  $g_1,\dots,g_m$  be  $\mathrm{MAJ}_{2m}$  gates where for  $k=1,\dots,m,$   $g_k$  takes as its input  $(y_1)_j(y_2)_j\cdots(y_m)_j1^{m-k+1}0^{k-1}$ . Clearly, the output  $g_1\cdots g_m=1^{\sum_{i=1}^m(y_i)_j}0^{m-\sum_{i=1}^m(y_i)_j}$ . For  $k=1,\dots,m-1$ , let  $g_k'=(g_k \text{ AND (NOT } g_{k+1}))$  and  $g_m'=g_m$ . Then  $g_k'$  evaluates to one if and only if  $\sum_{i=1}^m(y_i)_j$  is k. Hence, the k-th bit of the  $\log(m+1)$ -bit binary representation of  $\sum_{i=1}^m(y_i)_j$  is obtained by taking the OR of gates in the set  $\{g_k'; k \in \{1,\dots,m\}$  and the k-th bit of the  $\log(m+1)$ -bit binary representation of k is onek. Thus to obtain the  $\log(m+1)$ -bit binary representation of k is onek. Thus to obtain the k-th bit of the k-th bit of the logk-th or k-th or gates, k-th or k-th or gates and k-th or k-th o

**Theorem 11** For any  $0 < \epsilon < 1$ , MAJ<sub>n</sub> is downward self-reducible to MAJ<sub>n</sub> $^{\epsilon}$  by a Dlogtime-uniform pure reduction of depth  $O(1/\epsilon)$  and size  $O(n^{1+\epsilon})$  consisting of a linear number of gates.

*Proof.* First, we prove the claim for  $\epsilon=1/2$  to illustrate the technique. For simplicity and clarity we mostly ignore rounding issues. We can view the input as n 1-bit integers  $a_1,\ldots,a_n$ . To determine the output of MAJ $_n$  we will compute the binary representation of the sum of these integers. The total sum will be obtained in several stages. Each stage will take as an input a sequence  $a_1,a_2,\ldots,a_m$  of integers and convert it into a shorter sequence of integers  $b_1,b_2,\ldots,b_{m'}$  having the same sum, i.e., m' < m and  $a_1 + a_2 + \cdots + a_m = b_1 + \cdots + b_{m'}$ . The first stage will start with the input as a sequence of 1-bit integers and the last stage will output a single integer representing the total sum of the input bits. As no integer at any stage can attain a value larger than n we can always truncate any number of more than  $\log(n+1)$ -bits to the  $\log(n+1)$  least significant bits. (If convenient we may also pad a binary representation of any number by leading zeros to  $\log(n+1)$ -bits.)

Stage 1:  $n \times 1$ -bit  $\to (2\sqrt{n}+6) \times \log(n+1)$ -bits. This stage takes a sequence of bits  $a_1, a_2, \ldots, a_n$  and outputs  $b_1, b_2, \ldots, b_{2\sqrt{n}+6}$ . Partition  $\{1, \ldots, n\}$  into sets  $S_1, S_2, \ldots, S_{2\sqrt{n}+6}$  of consecutive integers, each set of size at most  $\sqrt{n}/2$ . Using Lemma 10 compute for each  $j=1,\ldots,2\sqrt{n}+6$  in parallel the integer  $b_j = \sum_{i \in S_j} a_i$ . Output  $b_1, \ldots, b_{2\sqrt{n}+6}$  padded to  $\log(n+1)$ -bits. Lemma 10 (with  $\ell=1$  and  $m=\sqrt{n}/2$ ) provides a circuit with at most  $2\sqrt{n}$  gates for computing each  $b_j$ , so in total we need O(n) of AND<sub>2</sub>, NOT and MAJ $\sqrt{n}$  gates for this stage.

Stage 2:  $(2\sqrt{n}+6) \times \log(n+1)$ -bits  $\to 5\lceil \log(n+1) \rceil \times \log(n+1)$ -bits. This stage takes a sequence of  $\log(n+1)$ -bit integers  $a_1, a_2, \ldots, a_{2\sqrt{n}+6}$  and outputs  $b_1, b_2, \ldots, b_{5\lceil \log(n+1) \rceil}$ . Similarly to the previous stage divide the  $a_i$ 's into five subsequences of size at most  $\sqrt{n}/2$  and using Lemma 10 (with  $\ell = \log(n+1)$  and  $m = \sqrt{n}/2$ , truncating the outputs to  $\log(n+1)$  bits), compute for each of the subsequences  $\log(n+1)$ -bit integers representing the sum of the  $a_i$ 's in that subsequence. Output all the  $5\lceil \log(n+1) \rceil$  integers that were obtained from the application of the lemma. Since each subsequence contains at most  $\sqrt{n}/2$  integers, this stage requires at most  $O(\sqrt{n}\log n)$  many  $AND_2$ , NOT and  $MAJ_{\sqrt{n}}$  gates.

Stage 3:  $5\lceil \log(n+1) \rceil \times \log(n+1)$ -bits  $\to 3 \times \log(n+1)$ -bits. This stage gets  $\log(n+1)$ -bit integers  $a_1, a_2, \ldots, a_{5\lceil \log(n+1) \rceil}$  and outputs  $b_1, b_2, b_3$ . It proceeds as follows. We divide the binary representation of each  $a_i, i \in \{1, \ldots, 5\lceil \log(n+1) \rceil\}$ , into blocks of  $\log \log n$  consecutive bits. Each block is regarded as a  $\log \log n$ -bit integer so we get integers  $a_{i,1}, a_{i,2}, \ldots, a_{i,k}$ , where  $k \approx \log(n+1)/\log\log n$  and  $a_i = \sum_{j=1}^k 2^{(k-j)\lceil \log\log n \rceil} a_{i,j}$ . For  $j=1,\ldots,k$ , we apply Lemma 10 on the sequence  $a_{1,j}, a_{2,j}, \ldots, a_{5\lceil \log(n+1) \rceil,j}$  to obtain

For  $j=1,\ldots,k$ , we apply Lemma 10 on the sequence  $a_{1,j},a_{2,j},\ldots,a_{5\lceil\log(n+1)\rceil,j}$  to obtain  $d_{j,1},d_{j,2},\ldots,d_{j,\log\log n}$ , where  $\sum_{i=1}^{5\lceil\log(n+1)\rceil}a_{i,j}=\sum_{i=1}^{\log\log n}d_{j,i}$ . Denote the value of the sum

$s_j$ . The sequence  $d_{j,1}, d_{j,2}, \ldots, d_{j,\log\log n}$  represents  $\log\log n$  integers, each having  $O(\log\log n)$  bits. Hence altogether they constitute only  $O(\log\log n)^2$  bits. Hence, using a DNF formula of size  $2^{O(\log\log n)^2} \le n^{o(1)}$  built from  $n^{o(1)}$  AND $_{O(\log\log n)^2}$  gates and a single  $\operatorname{OR}_{n^{o(1)}}$  gate we can calculate from the sequence  $d_{j,1}, d_{j,2}, \ldots, d_{j,\log\log n}$  each bit of the binary representation of  $s_j$ . For all j we do the whole calculation in parallel.

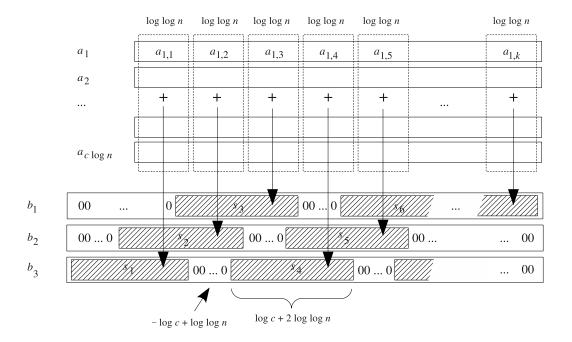

Finally, each  $s_j$  represents a sum of at most  $5\lceil \log(n+1) \rceil$  integers each of  $\log \log n$ -bits, so it can be represented by  $\log(5\lceil \log(n+1) \rceil + 1) + \log \log n \le 5 + 2\log \log n$  bits. We can form three integers  $b_1, b_2, b_3$  from  $s_1, \ldots, s_k$  that represent the sum of the  $a_i$ 's (see Fig. 1). Formally,  $b_i = \sum_{j \equiv 4-i \bmod 3} 2^{(k-j)\lceil \log \log n \rceil} s_j$ , where j ranges from 1 to k.

This stage involves  $O(\log n/\log\log n)$  applications of Lemma 10 with parameters  $\ell$  and m of order less than  $\log n$ , and  $k(5+2\log\log n)$  DNF formulas of size  $n^{o(1)}$ . Hence, it can be implemented by a constant-depth circuit consisting of a linear number of AND<sub>2</sub>, NOT and MAJ<sub> $n^{o(1)}$ </sub> gates.

Figure 1: Adding  $(k \log \log n)$ -bit integers  $a_1, a_2, \ldots, a_{c \log n}$ :  $b_1 + b_2 + b_3 = a_1 + a_2 + \cdots + a_{c \log n}$ .

Stage 4:  $3 \times \log(n+1)$ -bits  $\to 1 \times \log(n+1)$ -bits. Adding two n-bit integers can be done by  $AC^0$  circuits using  $O(n^2)$  many  $AND_n$ ,  $OR_n$  and NOT gates (see, e.g. [50, Theorem 1.15]). Hence, adding three  $\log(n+1)$ -bit integers can be done by constant-depth circuits using  $O(\log^2 n)$  many  $AND_{\log(n+1)}$ ,  $OR_{\log(n+1)}$  and NOT gates. Thus summing the input  $a_1, a_2, a_3$  of this stage can be done by a constant-depth circuit using  $O(\log^2 n)$  many  $MAJ_{O(\log n)}$  and NOT gates to obtain the final sum.

The resulting total sum obtained from Stage 4 of the circuit can be compared with the binary representation of n/2 by an  $AC^0$  circuit consisting of  $O(\log^2 n)$  many  $AND_{\log(n+1)}$ ,  $OR_{\log(n+1)}$  and NOT gates or alternatively  $MAJ_{O(\log n)}$  and NOT gates. As each stage of the computation can be done by constant-depth circuits consisting of a linear number of  $AND_2$ , NOT and  $MAJ_{\sqrt{n}}$  gates the lemma follows for  $\epsilon=1/2$ .

For general  $\epsilon$  the computation proceeds similarly, but the first two stages are replaced by a repeated use of a stage that reduces the input sequence  $a_1, a_2, \ldots, a_m$  to the sequence  $b_1, b_2, \ldots, b_{m'}$ , for  $m' = (2m \log(n+1))/n^{\epsilon}$ . The reduction is done using Lemma 10 applied on subsequences of  $a_i$ 's of length  $n^{\epsilon}/2$ . Once  $m' \leq n^{\epsilon}/2$ , a single application of Lemma 10 produces  $\log(n+1)$  integers that can be passed to the last two stages of the above procedure. Clearly,  $2+1/\epsilon$  repetitions will suffice for the first stage, each repetition requiring at most  $n^{1-\epsilon} \cdot O(n^{\epsilon}) = O(n)$  gates for MAJ $_{n^{\epsilon}}$ , AND $_2$  and NOT.

We have established that the self-reductions have a linear number of gates, but it remains for us to prove the size bound of  $O(n^{1+\epsilon})$  by counting the number of wires. There are O(n) gates, each having fan-in at most  $n^{\epsilon}$ . Thus the total size is  $O(n^{1+\epsilon})$ . Dlogtime-uniformity of the circuit is routine to establish.

We have seen that AND, OR, MOD-q, and MAJ are all downward self-reducible. We saw also that downward self-reducibility holds for the word problem over any finite monoid, which yields self-reductions for some of the standard complete problems for NC<sup>1</sup>: W5-STCONN and the word problem over  $S_5$ . We thank Mario Szegedy for pointing out that BFE (another standard complete problem for NC<sup>1</sup>) is also downward self-reducible:

**Proposition 12** For any  $0 < \epsilon < 1$ , BFE<sub>n</sub> is downward self-reducible to BFE<sub>n</sub> by a Dlogtime-uniform pure reduction of depth  $O(1/\epsilon)$  and size O(n).

*Proof.* We will show that there is a constant c and an oracle circuit family  $\{C_n\}_{n\geq 1}$  such that  $C_n$  is a pure reduction of depth c and size O(n) reducing BFE<sub>n</sub> to BFE<sub>4n<sup>1/2</sup></sub>, where no path from a leaf to the root of  $C_n$  encounters more than two oracle gates.

We first show that this suffices to prove the proposition. Note that if we replace each oracle gate for  ${\rm BFE}_m$  in  $C_n$  by the oracle circuit  $C_m$ , we obtain a Dlogtime-uniform family of pure reductions of depth 3c and size O(n) reducing  ${\rm BFE}_n$  to  ${\rm BFE}_{16n^{1/4}}$ , where no path from a leaf to the root of  $C_n$  encounters more than four oracle gates. (Notice, each oracle gate for  ${\rm BFE}_m$  uses O(m) wires and is replaced by a circuit having also O(m) wires. Thus, the size of the circuit gets at most multiplied by some constant.) By induction, we obtain, for every k, a Dlogtime-uniform family of pure reductions of depth  $(2^k-1)c$  and size O(n) reducing  ${\rm BFE}_n$  to  ${\rm BFE}_{4k_n n^{1/2}k}$ .

Thus, in particular, for  $\epsilon$  of the form  $1/2^{k-1}$  there is a Dlogtime-uniform family of pure reductions of depth  $(2^k-1)c=O(1/\epsilon)$  and size O(n) reducing BFE $_n$  to BFE $_{n^{1/\epsilon}}$ , since  $4^kn^{1/2^k}< n^{1/2^{k-1}}$  for all large n. The theorem follows, since every  $\epsilon$  is within a factor of 2 of some smaller number of the form  $1/2^{k-1}$ .

We now proceed to prove the claim, by presenting the circuit family  $\{C_n\}$ . BFE contains only inputs of length n of the form  $n=2^{d+1}-1$  for some integer d, so assume n has this form. Assume that d is odd; the construction is simpler if d is even. Let us denote the first  $2^d-1$  input symbols by v, and the last  $2^d$  input symbols by x.

The output gate of  $C_n$  will be an AND gate of fan-in two, where one child a checks if the input is a well-formed formula, and the other child b evaluates the formula, assuming that it is well-formed. We consider b first.

The gate b is an oracle gate that has as its input the string v'x', where v' consists of the first  $2^{(d+1)/2}-1$  symbols of v, and x' is a string of 2(d+1)/2 symbols consisting of the outputs of oracle gates  $b_i$ , for  $1 \le i \le 2^{(d+1)/2}$ . If the input string vx is well-formed, the string v' encodes the subformula of the formula v having depth roughly half of the depth of v and containing the output gate of v, and the oracle gates  $b_i$  will evaluate the subformulas of v that feed into v'. More precisely, the oracle gate  $b_i$  will take as input a string  $(v_i, x_i)$ , where  $v_i$  is the i-th block of length  $2^{(d-1)/2}-1$  after v' in v, and  $x_i$  is the i-th block of length  $2^{(d-1)/2}$  in x. It is immediate that the gate b produces the desired output, if the input is a well-formed formula. A routine calculation shows that the queries have length bounded by  $4n^{1/2}$ .

We now turn to the construction of the subcircuit a that tests if the input is well-formed. Recall that the input is well-formed if and only if  $v \in \{\land, \lor, \oplus\}^*$  and  $x \in \{0, 1\}^*$ . This is simply an AND of

n conditions (call them  $c_i$ ), where each condition  $c_i$  can be computed using NC<sup>0</sup> circuitry. We need to evaluate this AND using oracle gates for BFE $_m$  where  $m \leq 4n^{1/2}$ . To do this, we first use another layer of NC<sup>0</sup> circuitry to halve the fan-in of the unbounded fan-in AND that we need to compute; we compute conditions  $c'_j$  defined by  $c'_j = c_{2j-1} \wedge c_{2j}$  for  $j = 1, \ldots, (n-1)/2$  and  $c'_{(n+1)/2} = c_n$ . Note that the input is well-formed if and only if BFE(v''x'') evaluates to true, where x'' consists of the bits  $c'_j$  and  $v'' = \wedge^{(n-1)/2}$ . This well-formed instance of BFE can be evaluated using queries to BFE $_m$  for  $m \leq 4n^{1/2}$ , using the same construction as was used for the gate b, to evaluate a formula.

To complete the proof, we merely observe that the number of wires is easily seen to be linear in n, and we note that Dlogtime-uniformity is routine to establish.

Indeed, we point out that any problem that is complete for a complexity class that has a strongly downward self-reducible complete problem must be strongly downward self-reducible. See Proposition 24.

Another problem for which we can prove downward self-reducibility is *Iterated Matrix Multiplication*. Let  $\mathrm{IMM}_{n,d,\ell}:\{0,1\}^{nd^2\ell}\to\{0,1\}^{d^2n(\ell+\log d)}$  be the problem of computing the product of  $n\ d\times d$  matrices, with each entry being a non-negative  $\ell$ -bit integer. Define the *modular* version of the Iterated Matrix Product to be the function  $\mathrm{mIMM}_{n,d,q}:\{0,1\}^{nd^2\log q}\to\{0,1\}^{d^2\log q}$  computing the Iterated Matrix Product modulo some integer  $q\geq 2$ . Finally, we will also need to consider the *Boolean* Iterated Matrix Product problem  $\mathrm{BIMM}_{n,d}:\{0,1\}^{nd^2}\to\{0,1\}^{d^2}$  which is the Iterated Matrix Problem over the ring  $(\{0,1\},\mathrm{OR},\mathrm{AND})$ .

The following proposition is immediate using the same technique as in Proposition 6:

**Proposition 13** For any  $0 < \epsilon < 1$  and any  $n, d, q \ge 1$ ,  $\operatorname{mIMM}_{n,d,q}$  is downward self-reducible to  $\operatorname{mIMM}_{n^{\epsilon},d,q}$  by a Dlogtime-uniform pure reduction of depth  $O(1/\epsilon)$  and size  $O(nd^2 \log q)$  using O(n) oracle gates for  $\operatorname{mIMM}_{\ell,d,q}$ ,  $n^{\epsilon/2} \le \ell \le n^{\epsilon}$ . Similarly  $\operatorname{BIMM}_{n,d}$  is reducible to  $\operatorname{BIMM}_{n^{\epsilon},d}$  by a reduction of depth  $O(1/\epsilon)$  and size  $O(nd^2)$  using O(n) oracle gates.

The following more interesting lemma will be useful in the next section.

**Lemma 14** There is a universal constant  $c_{CRR}$  such that for any  $0 < \epsilon < 1$  and any  $d(n) \le n$ ,  $IMM_{n,d(n),n}$  is downward self-reducible to  $IMM_{n^{\epsilon},d(n),n^{\epsilon}}$  by a Dlogtime-uniform  $TC^0$ -reduction of depth  $O(1/\epsilon)$  and size  $O(d(n)^2 \cdot n^{3+2c_{CRR}})$  using  $O(n^3)$  oracle gates.

Here,  $c_{\rm CRR}$  is a specific constant that can be determined from a paper of Hesse et al. [31]. The exact value of  $c_{\rm CRR}$  is not important for our purposes, but we estimate that  $c_{\rm CRR} < 10$ . *Proof.* Hesse et al. [31] give Dlogtime-uniform  $TC^0$  circuits with  $O(n^{c_{\rm CRR}})$  wires that do the following tasks:

- take as input two n-bit integers a and b, and output  $a \mod b$ . (Call this circuit  $A_n$ .)

- take as input an n-bit integer a, and output its *Chinese Remainder Representation*, i.e., a sequence of n pairs  $(a_i, b_i)$  of  $O(\log n)$ -bit numbers where  $a_i = a \mod b_i$  and all  $b_i$  are distinct primes depending only on n. (Call this circuit  $B_n$ .)

- take as input n pairs  $(a_i, b_i)$  of  $O(\log n)$ -bit numbers and output an  $O(n \log n)$ -bit number a satisfying  $a_i = a \mod b_i$  and  $0 \le a < \prod_i b_i$ , if the  $b_i$  are distinct primes. (Call this circuit  $R_n$ .)

Let n be large enough and set d=d(n). Using these three circuit families we can reduce  $\mathrm{IMM}_{n,d,n}$  to the problem of computing  $O(n^2)$  instances of  $\mathrm{mIMM}_{n,d,q_i}$  in parallel for  $O(n^2)$  distinct prime  $O(\log n)$ -bit numbers  $q_i$ . Namely to compute the iterated product, we first compute the Chinese Remainder Representation of each input matrix; this gives us  $O(n^2)$  instances of  $\mathrm{mIMM}_{n,d,q_i}$  to solve. Next, we compute the iterated product mod each of the  $q_i$  (thereby obtaining the output in

Chinese Remainder Representation). Finally, we convert the answer to binary representation. The following three steps describe the computation in more detail.

**Step 1.** We convert the input matrices  $M_1, M_2, \ldots, M_n$  into  $2n^2 \ge n(n + \log d)$  sequences of  $d \times d$  matrices  $M_{1,j}, M_{2,j}, \ldots, M_{n,j}, j \in \{1, 2, \ldots, 2n^2\}$  as follows: For each  $i \in \{1, \ldots, n\}$  and  $k, \ell \in \{1, \ldots, d\}$  we apply the circuit  $B_{2n^2}$  on the entry  $(M_i)_{k,\ell}$  of  $M_i$  padded by leading zeros to  $2n^2$  bits, to obtain  $((M_{i,1})_{k,\ell}, q_1), ((M_{i,2})_{k,\ell}, q_2), \ldots, ((M_{i,2n^2})_{k,\ell}, q_{2n^2})$ . That is, each matrix  $M_{i,j}$  consists of the entries of  $M_i$  modulo the  $O(\log n)$ -bit prime  $q_j$ . This step consists of  $n \cdot d^2$  copies of circuit  $A_{2n^2}$  so it can be done by a  $TC^0$  circuit of size  $O(d^2n^{1+2c_{\mathrm{CRR}}})$ .

Step 2. For each  $j \in \{1, 2, \dots, 2n^2\}$ , we compute the product  $N_j$  of matrices  $M_{1,j}, M_{2,j}, \dots, M_{n,j}$  mod  $q_j$ . To do so, we use the pure self-reduction of  $\operatorname{mIMM}_{n,d,q_j}$  to  $\operatorname{mIMM}_{n^\epsilon,d,q_j}$  given by Proposition 13. However as we do not have oracle access to  $\operatorname{mIMM}_{n^\epsilon,d,q_j}$ , we replace each oracle gate for  $\operatorname{mIMM}_{\ell,d,q_j}, n^{\epsilon/2} \leq \ell \leq n^\epsilon$ , by a small sub-circuit consisting of an oracle gate  $\operatorname{IMM}_{\ell,d,\ell}$  giving an intermediate matrix M followed by an application of the circuit  $A_{2\ell^2}$  on each entry of M (padded by leading zeros to  $2\ell^2$  bits) to obtain  $M \operatorname{mod} q_j$ , i.e., the result expected from the oracle gate  $\operatorname{mIMM}_{\ell,d,q_j}$ . Thus, to compute  $N_j$ , we use a  $\operatorname{TC}^0$  circuit with O(n) oracle gates for  $\operatorname{IMM}_{\ell,d,\ell}, n^{\epsilon/2} \leq \ell \leq n^\epsilon$ ,  $O(nd^2)$  copies of  $A_{2\ell^2}$ , and  $O(nd^2\log n)$  wires for the original self-reduction. In total to implement this step we need  $O(n^3)$  oracle gates for  $\operatorname{IMM}_{\ell,d,\ell}$  and  $n^2 \cdot O(nd^2\log n + nd^2n^{2\epsilon_{\mathrm{CCRR}}} + d^2n^{2\epsilon}) = O(n^{3+2\epsilon_{\mathrm{CCRR}}}d^2)$  wires.

**Step 3.** From the previous step we obtain matrices  $N_1, N_2, \ldots, N_{2n^2}$  which represent the product N of matrices  $M_1, \ldots, M_n$ . Here,  $N_j = N \mod q_j$ . For each  $k, \ell \in \{1, \ldots, d\}$  apply the circuit  $R_{2n^2}$  on  $((N_1)_{k,\ell}, q_1), ((N_2)_{k,\ell}, q_2), \ldots, ((N_{2n^2})_{k,\ell}, q_{2n^2})$  to obtain the entry  $N_{k,l}$  of N. This step requires  $d^2$  copies of  $R_{2n^2}$ , so in total it uses  $O(d^2n^{2c_{\mathrm{CRR}}})$  wires.

The desired circuit for  $\mathrm{IMM}_{n,d,n}$  is obtained by combining the above three steps. Clearly, the circuit will use  $O(n^3)$  oracle gates for  $\mathrm{IMM}_{\ell,d,\ell}$ ,  $\ell \leq n^\epsilon$  and  $O(d^2(n^{3+2\epsilon c_{\mathrm{CRR}}}+n^{1+2c_{\mathrm{CRR}}}))$  wires.

4 Amplifying lower bounds

In the previous section we have established several downward self-reducibility results. In this section we show that any problem that is downward self-reducible in this way has circuits of polynomial size of some type if and only if it has very small circuits of that type. Thus, if a small circuit size lower bound can be proved for any such problem, it can be "amplified" into a superpolynomial size lower bound.

The general form of our claims is:

If a function f is computable by polynomial-size circuits of type  $\mathcal{C}$  then for any  $\epsilon > 0$ , f is computable by circuits of type  $\mathcal{C}$  using  $O(n^{1+\epsilon})$  gates and wires.

The circuit types we will consider are  $AC^0$ ,  $ACC^0$ ,  $CC^0$ ,  $TC^0$  and  $NC^1$  circuits. The functions f we will consider will typically (but not always) be complete for some complexity class. For example MAJ is complete for  $TC^0$  (under  $\leq_T^{NC^0}$  reductions), and the word problem for  $S_5$  is complete for  $NC^1$ , and so on. The consequence of our claim is that establishing a lower bound of  $\Omega(n^{1+\epsilon})$  for some  $\epsilon>0$  on the number of wires or gates necessary to compute f would separate some of the circuit classes. The following proposition summarizes known relationships between these circuit classes.

#### **Proposition 15**

$$AC^0 \subsetneq ACC^0 \subseteq TC^0 \subseteq NC^1$$

$CC^0 \subseteq ACC^0, CC^0 \not\subseteq AC^0$

Except for the proper inclusion  $AC^0 \subsetneq ACC^0$  [25, 52, 30] which also implies  $CC^0 \not\subseteq AC^0$  the precise relationship among  $ACC^0$ ,  $CC^0$ ,  $TC^0$  and  $NC^1$  is not known, and any separation or collapse would constitute major progress in theoretical computer science. Separation of, say,  $TC^0$  from  $NC^1$  would typically entail showing that no polynomial-size  $TC^0$  circuit family can compute some chosen function from  $NC^1$ . We show that this same separation follows already from a much smaller lower bound.

**Theorem 16** Let C be one of the circuit classes considered above (and the class of associated functions), and f be a function. If for some  $\epsilon_0$  and  $s(n): \mathcal{N} \to \mathcal{N}$ , for every  $0 < \epsilon \le \epsilon_0$ ,  $f_n$  is downward self-reducible to  $f_{n^{\epsilon}}$  by a pure reduction of depth  $O(1/\epsilon)$  and size O(s(n)), and f has polynomial-size circuits of type C, then for every  $\epsilon' > 0$ , f has circuits of type C of size  $O(s(n)n^{\epsilon'})$ .

*Proof.* Assume that  $f_n$  has circuits of type  $\mathcal C$  with  $n^k+k$  wires. Let  $\epsilon=\min(\epsilon'/k,\epsilon_0)$ . Consider the reduction of  $f_n$  to  $f_{n^\epsilon}$  that is of size O(s(n)) and hence has at most O(s(n)) oracle gates. If we replace each oracle gate for  $f_{n^\epsilon}$  by the circuit of type  $\mathcal C$  of size  $n^{\epsilon k}+k$ , we obtain a circuit of type  $\mathcal C$  for  $f_n$  with  $O(s(n)n^{\epsilon k})=O(s(n)n^{\epsilon'})$  wires. The claim follows. (Technically, class  $\mathcal C$  may not allow for bounded fan-in AND, OR or NOT gates which may appear in the pure reduction hence, one needs to simulate such gates by constant-size circuits of type  $\mathcal C$ . However, this simulation does not affect the size bound by more than a constant factor.)

By analyzing the depth of the circuits constructed in the proof of Theorem 16, one can observe that if  $\mathcal{C}$  is a class of *bounded depth* circuits, then f has circuits of type  $\mathcal{C}$  having depth  $O(1/\epsilon')$  and  $O(s(n)n^{\epsilon'})$  wires. For most of our arguments, for any  $\epsilon_0 < 1$ , either s(n) = n or  $s(n) = n^{1+\epsilon_0}$ . This yields the following corollary.

**Corollary 17** 1. If for some  $\epsilon > 0$ , W5-STCONN requires  $CC^0$  circuits with at least  $\Omega(n^{1+\epsilon})$  wires, then  $CC^0 \neq NC^1$ . The same is true with  $ACC^0$  and  $TC^0$  in place of  $CC^0$ , and with BFE and  $W_{S_5}$  in place of W5-STCONN.

- 2. If for some  $\epsilon > 0$ , MAJ requires  $CC^0$  circuits with at least  $\Omega(n^{1+\epsilon})$  wires then  $CC^0 \neq TC^0$ . The same is true with  $ACC^0$  in place of  $CC^0$ .

- 3. If for some  $\epsilon > 0$ , AND requires  $CC^0$  circuits with at least  $\Omega(n^{1+\epsilon})$  wires then  $CC^0 \neq ACC^0$ .

Contrast this with the situation for SAT; if SAT is in  $TC^0$ , we have no way to bound the number k such that  $TC^0$  size  $n^k$  is sufficient to compute SAT. (Although, as we mentioned in Section 1.2, Srinivasan has shown that if P = NP then there are algorithms running in time  $n^{1+\epsilon}$  that compute weak approximations to MAX-CLIQUE [47]. See also our Section 6.)